Elpida Completes Development of Cu-TSV (Through Silicon Via) Multi-Layer 8-Gigabit DRAM

Elpida Memory today announced that it has completed development of a Cu-TSV (Through Silicon Via) multi-layer 8-Gigabit DRAM.

TSV is three-dimensional packaging technology, which involves stacking multi chips vertically through electrical connections with metal-filled via holes. Compared with the existing connection method of wire bonding multiple chips, TSV drastically reduces the wire distance, which enables faster speeds, lower power consumption and smaller package size. Elpida began developing TSV in 2004 based on a Grant Program provided by the New Energy and Industrial Technology Development Organization (NEDO), a research endeavor founded by the Japanese government. Since then Elpida has continued to develop TSV technology.

In preparation for TSV products manufacturing, Elpida has installed a manufacturing line for TSV at the Hiroshima Plant and will make use of Akita Elpida's package processing to conduct full scale production in Japan.

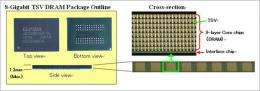

The newly developed TSV DRAM consists of eight 1-Gigabit DDR3 SDRAM chips that total 8-Gigabit and an interface chip. This TSV-processed 8-Gigabit DRAM uses only one-fourth the standby power compared with MCP (Multi- Chip Package) and PoP (Package on Package). Applications of TSV products to high-density modules can reduce power consumption of servers, data centers and other high-capacity memory systems. Also, a multi-layer DRAM not only achieves higher density but may also soon enable combined logic/DRAM high-end three-dimensional multi-layer chips based on a TSV with an extremely large number of interconnects.

"TSV is a key technology to realize Elpida's total memory solution strategy. To take advantage of TSV wide-bit interconnects, not only ultra-high-density DRAM, we will also develop logic/DRAM combined chips to enable high-performance, low-power system chips." said Takao Adachi, Chief Technology Officer of Elpida Memory, Inc.

Elpida's TSV multi-layer technology development success has moved the company to within sight of beginning mass production of TSV multi-layer products. Sample shipments of the 8-Gigabit TSV DRAM are scheduled to start before the end of 2009 and sample 16-Gigabit products (2-Gigabit eight-layer DRAM products) will begin in mid 2010.

Special features of the newly developed 8-Gigabit TSV DRAM:

• JEDEC-compliant 8-Gigabit DDR3 SDRAM (operating at 1,600Mbps)

• Number of connections between core layers: 1,030 connections

(8,357 bump connections for a single package, including the interface layer)

• Package height: 1.3mm (maximum), including eight core layers and one interface layer.

Also, possible TSV application products:

• Ultra high-density DRAM modules (for use in supercomputers and servers)

• DRAM/logic combined chip to enable high-performance mobile devices

• High-end graphics chips for use in high-performance digital consumer electronics and game consoles

Source: Elpida Memory